| КР1802ВР3 | |||||||

| Параллельный умножитель 8*8 разрядов | |||||||

| |||||||

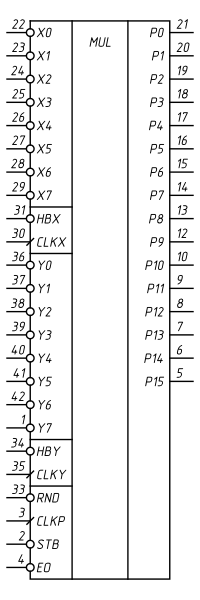

Микросхема КР1802ВР3 представляет собой параллельный умножить 8*8 разрядов, предназначенный для умножения кодов (чисел без знака) и чисел со знаком, представленных в дополнительном коде. Числа могут быть как целыми, так и меньше единицы. Умножитель является устройством модульного типа, обеспечивающим построение умножителей с любой разрядностью операндов, кратной 8.

Множимое, подаваемое на шину X0 - X7, и множитель, поступающий на шину Y0 - Y7, запоминаются соответственно в регистре множимого и регистре множителя. Регистры выполнены на D-триггерах с записью информации по фронту сигналов CLKX и CLKY соответственно. Управляющие сигналы HBX и HBY указывают, что умножение производится над кодами (при высоком уровне напряжения на входах HBX и HBY) или над числами со знаком, представленных дополнительным кодом (при низком уровне напряжения на входах HBX и HBY).

Блок умножения представляет собой комбинационную схему, выполняющую умножение двух 8-разрядных чисел и одновременное округление результата. Округление произведения до 16 разрядов выполняется при установке триггера округления в "1", что осуществляется по фронту сигнала CLKX или CLKY при наличии на входе RND "Округление" напряжения высокого уровня.

Результат умножения по фронту сигнала CLKP и при наличии сигнала STB "Управление записью в регистр произведения" записывается в 16-разрядный регистр произведения и через выходной буфер, управляемый сигналом EO "Разрешение выдачи", выдаётся на выходную шину P0 - P15. При подаче на управляющий вход EO сигнала высокого уровня, выходной буфер устанавливается в состояние "Выключено".

Основные параметры микросхемы

Время умножения 8-разрядных чисел - не более 130 нс.

Потребляемая мощность - не более 1350 мВт.