# Marias The State of Maria Specification Same 8218/8219 **BIPOLAR MICROCOMPUTER BUS** CONTROLLERS FOR MCS-80™ AND MCS-85™ FAMILIES

- 8218 for Use in MCS-80<sup>™</sup> Systems

- 8219 for Use in MCS-85<sup>™</sup> Systems

- Coordinates the Sharing of a Common **Bus Between Several CPU's**

- **■** Reduces Component Count in **Multimaster Bus Arbitration Logic**

- Single +5 Volt Power Supply

- 28 Pin Package

The 8218 and 8219 Microcomputer Bus Controllers consist of control logic which allows a bus master device such as a CPU or DMA channel to interface with other masters on a common bus, sharing memory and I/O devices. The 8218 and 8219

- 1. Bus Arbitration Logic which operates from the Bus Clock (BCLK) and resolves bus contention between devices sharing

- 2. Timing Logic which when initiated by the bus arbitration logic generates timing signals for the memory and I/O command lines to guarantee set-up and hold times of the address/data lines onto the bus. The timing logic also signals to the bus arbitration logic when the current data transfer is completed and the bus is no longer needed.

- 3. Output Drive Logic which contains the logic and output drivers for the memory and I/O command lines.

An external RC time constant is used with the timing logic to generate the guaranteed address set-up and hold times on the bus. The 8219 can interface directly to the 8085A CPU and the 8218 interfaces to the 8080A CPU chip and the 8257 DMA controller.

#### **BLOCK DIAGRAM** PIN CONFIGURATION BUSY BREQ BCR1 INIT 28 Vcc BPRN 27 OVRD BUS ARBITRATION N.C. [ BPRO 26 RSTB RSTB XSTR [ INIT XCP [ 25 BCR1 ADEN XCY [ 24 🔲 (E) BCLK OVED 23 BPRO (A) 6 BPRN (B) [ 22 8218/8219 (C) 8 21 BREO DLYADJ -20 BCLK (D) 9 ANYR 🔲 10 ADEN 19 BUSY RDD 11 18 TO THE TO THE XSTR TIMING LOGIC lowc MRDC [ 17 12 MASTER IORC [ MWTC 13 16 XCP DLYADJ GND [ 15 XCY · ANYR -MRDC 8219 (A) IOWR (B) WWTR ► MWTC 10/M (B) OUTPUT DRIVE LOGIC IORC IORR RD ASRO (D) MRDR - IOWC BCR2 (D) RDD N.C. = NO.CONNECT

## **8218/8219 PIN DEFINITIONS**

## Signals Interfaced Directly to the System Bus

#### **BREQ (TTL Output)**

The Bus-Request is used with a central parallel priority resolution circuit. It indicates that the device needs to access the bus for one or more data transfers. It is synchronized with the Bus Clock.

#### **BUSY** (Input, O.C. Output)

Bus-Busy indicates to all master devices on the bus that the bus is in use. It inhibits any other device from getting the bus. It is synchronized with Bus Clock.

#### **BCLK** (Input)

The negative edge of Bus-Clock is used to synchronize the bus contention resolution circuit asynchronously to the CPU clock. It has 100ns min. period, 35%-65% duty cycle. It may be slowed, single stepped or stopped.

#### **BPRN** (Input)

The Bus-Priority-In indicates to a device that no device of a higher priority is requesting the bus. It is synchronous with the Bus Clock.

#### **BPRO (TTL Output)**

The Bus-Priority-Out is used with serial priority resolution circuits. Priority may be transferred to the next lower in priority as BPRN.

#### INIT (Input)

The Initialize resets the 8218/8219 to a known internal state.

#### MRDC (3-State Output)

The Memory-Read-Control indicates that the Master is requesting a read operation from the addressed location. It is asynchronous to the Bus Clock.

#### MWTC (3-State Output)

The Memory-Write-Control indicates that data and an address have been placed on the bus by the Master and the data is to be deposited at that location. It is asynchronous to the Bus Clock.

#### **IORC** (3-State Output)

The I/O-Read-Control indicates that the Master is requesting a read operation from the I/O device addressed. It is asynchronous to the Bus Clock.

### IOWC (3-State Output)

The I/O-Write-Control indicates that Data and an I/O device address has been placed on the bus by the Master and the data is to be deposited to the I/O device.

## Signals Generated or Received by the Bus Master

#### BCR1/BCR2 (Inputs)

Bus-Control-Request 1 or Bus-Control-Request 2 indicate to the 8218/8219 that the Master device is making a request to control the bus. BCR2 is active low in the 8218 (BCR2). BCR2 is active high in the 8219.

#### **RSTB** (Input)

Request-Strobe latches the status of BCR1 and BCR2 into the 8218/8219. The strobe is active low in the 8218 and negative edge triggered in the 8219.

#### **ADEN (TTL Output)**

Address-and-Data-Enable indicates the Master has control of the bus. It is often used to enable Address and Data Buffers on the bus. It is synchronous with Bus

#### RDD (TTL Output)

Read-Data controls the direction of the bi-directional data bus drivers. It is asynchronous to the Bus Clock. A high on RDD indicates a read mode by the master.

#### **OVRD** (Input)

Override inhibits automatic deselect between transfers caused by a higher priority bus request. May be used for consecutive data transfers such as read-modify-write operations. It is asynchronous to the Bus Clock.

#### XSTR (Input, Rising-Edge-Triggered)

Transfer-Start-Request indicates to the 8218/8219 that a new data transfer cycle is requested to start. It is raised for each new word transfer in a multiple data word transfer. It is asynchronous to the Bus Clock.

#### XCP (Input, Falling-Edge-Triggered)

Transfer-Complete indicates to the 8218/8219 that the data has been received by the slave device in a write cycle or transmitted by the slave and received by master in a read cycle. It is asynchronous to the Bus Clock.

#### XCY (TTL Output)

Indicates that a data transfer is in progress. It is asynchronous to the Bus Clock.

#### $\overline{WR}$ , $\overline{RD}$ , $\overline{IO/M}$ (8219 Only) (Inputs from 8085 to the 8219)

WRITE, READ, IO/Memory are the control request inputs used by the 8085 and are internally decoded by the 8219 to produce the request signals MRDR, MWTR, IORR, IOWR. They are asynchronous to the Bus Clock.

#### ASRQ (8219 Only) (Input from 8085 System)

Can be used for interrupt status from the 8085. Acts like a level sensitive asynchronous bus request — no RSTB needed. It is asynchronous to the Bus Clock.

#### MRDR, MWTR, IORR, IOWR (8218 Only) (Inputs from 8080 or 8257 to the 8218)

Memory-Read-Request, Memory-Write-Request, Read-Request, or I/O-Write-Request indicate that address and data have been placed on the bus and the appropriate request is being made to the addressed device. Only one of these inputs should be active at any one time. They are asynchronous to the Bus Clock.

## **ANYR (TTL Output)**

Any-Request is the logical OR of the active state of MRDR, MWTR, IORR, IOWR. It may be tied to XSTR when the rising edge of ANYR is used to initiate a transfer.

#### **DLYADJ** (Input)

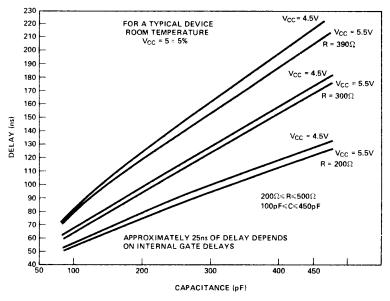

Delay-Adjust is used for connection of an external capacitor and resistor to ground to adjust the required set-up and hold time of address to control signal.

#### 8218/8219 FUNCTIONAL DESCRIPTION

The 8218/8219 is a bipolar Bus Control Chip which reduces component count in the interface between a master device and the system Bus. (Master device: 8080, 8085, 8257 (DMA).)

The 8218 and 8219 serve three major functions:

- 1. Resolve bus contention.

- Guarantee set-up and hold time of address/data lines to I/O and Memory read/write control signals (adjustable by external capacitor).

- 3. Provide sufficient drive on all bus command lines.

## **Bus Arbitration Logic**

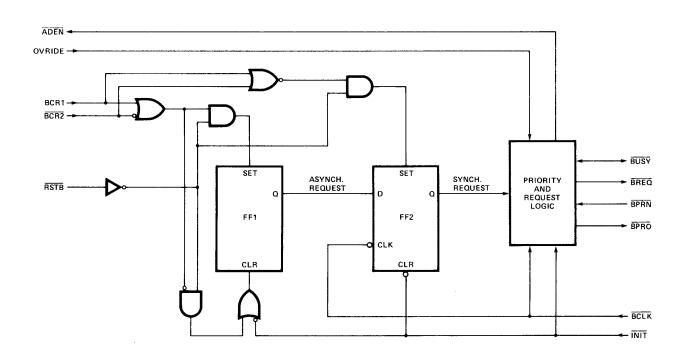

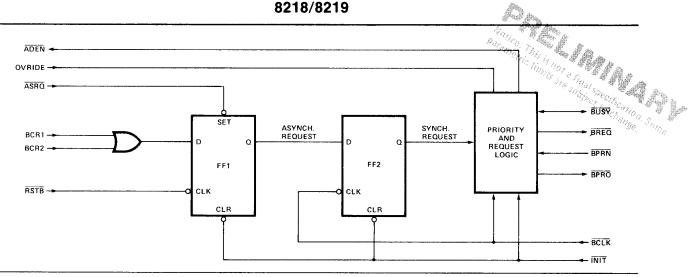

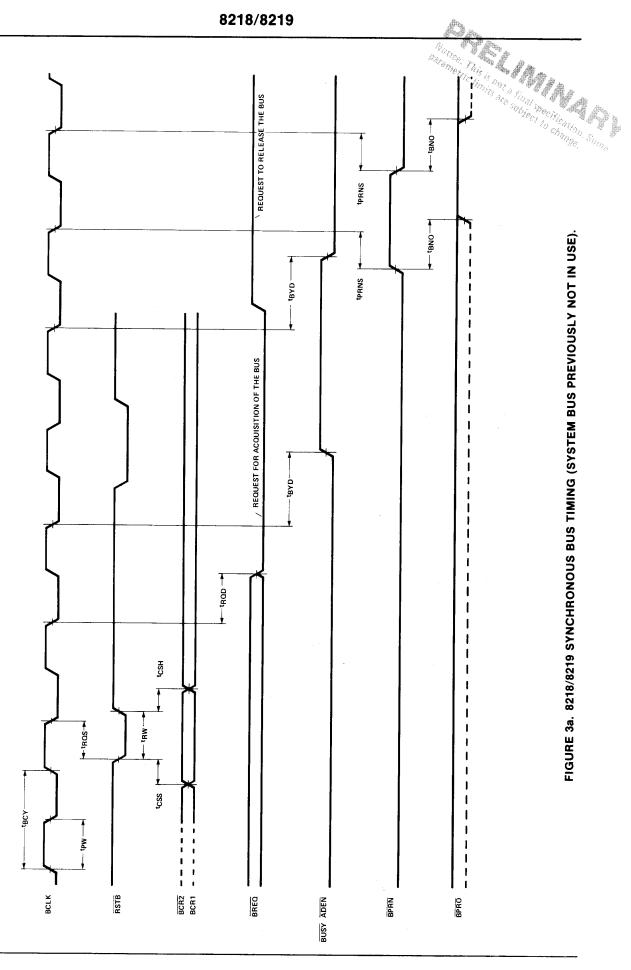

Bus Arbitration Logic activity begins when the Master makes a request for use of the bus on BCR1 or BCR2. The request is strobed in by RSTB. Following the next two falling edges of the bus clock (BCLK) the 8218/8219

outputs a bus request (BREQ) and forces Bus Priority Out inactive (BPRO). See Figures 1a and 1b.

BREQ is used for requesting the bus when priority is decided by a parallel priority resolver circuit.

BPRO is used to allow lower priority devices to gain the bus when a serial priority resolving structure is used.

BPRO would go to BPRN of the next lower priority Master.

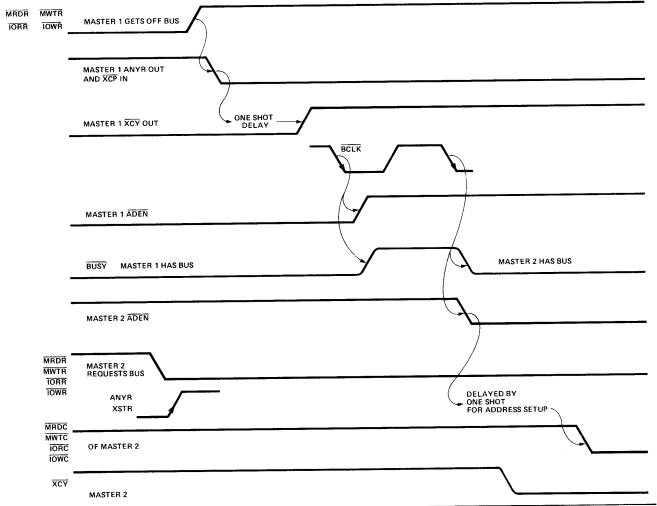

When priority is granted to the Master (a low on BPRN and a high on BUSY) the Master outputs a BUSY signal on the next falling edge of BCLK. The BUSY signal locks the master onto the bus and prohibits the enable of any other masters onto the bus.

At the same time BUSY goes active, Address and Data Enable (ADEN) goes active signifying that the Master has control of the bus. ADEN is often used to enable the bus drivers.

The Bus will be released only if the master loses priority; is not in the middle of a transfer, and Override is not active or, if the Master stops requesting the bus, is not in the middle of a data transfer, and Override is not active. ADEN then goes inactive.

Provision has been made in the 8218 to allow bussynchronous requests. This mode is activated when BCR1, BCR2 and RSTB are all low. This action asynchronously sets the synchronization flip flop (FF2) in Figure 1a.

FIGURE 1a. 8218 BUS ARBITRATION LOGIC

FIGURE 1b. 8219 BUS ARBITRATION LOGIC

#### **Timing Logic**

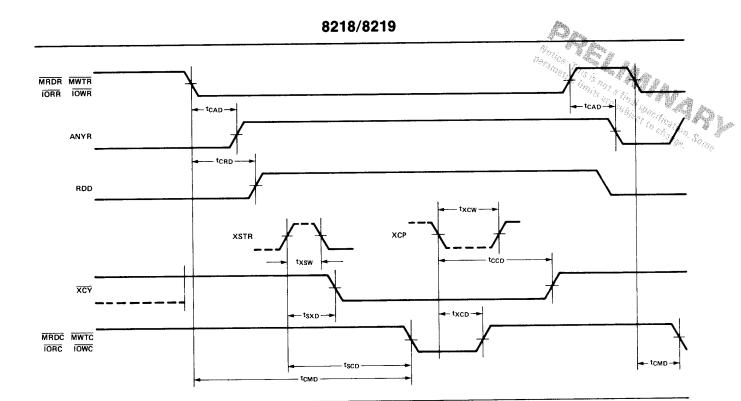

Timing Logic activity begins with the rising edge of XSTR (Transfer Start Request) or with ADEN going active, whichever occurs second. This action causes XCY (Transfer Cycle) to go active. 50-200ns later (depending on resistance and capacitance at DLYADJ) the appropriate Control Outputs will go active if the control input is active.

XSTR can be raised after the command goes active in the current transfer cycle so that a new transfer can be initiated immediately after the current transfer is complete.

A negative going edge on XCP (Transfer Complete) will cause the Control Outputs (MRDC, etc.) to go inactive. 50-200ns later (depending on capacitance at DLYADJ) XCY will go inactive indicating the transfer cycle is completed.

Additional logic within the 8218/8219 guarantees that if a transfer cycle is started (XCY is active), but the bus is not requested (BREQ is inactive) and there is no command request input (ANYR is output low), then the transfer cycle will be cleared. This allows the bus to be released in applications where advanced bus requests are generated but the processor enters a HALT mode.

## **Control Logic**

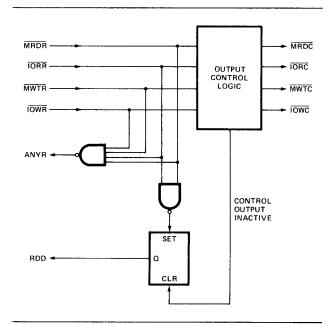

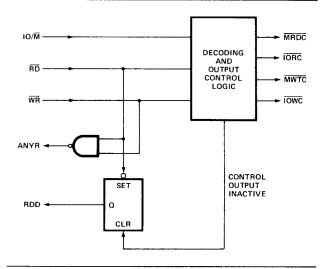

The control outputs are generated in the 8219 by decoding the 8085 system control outputs (i.e., RD, WR, IO/M) or in the 8218 by directly buffering the control inputs to the control outputs for use in an 8080 or DMA system (see Figures 2a and 2b). The control outputs may be held high (inactive) by the Timing Logic. Also the control outputs are enabled when the Master gains control of the bus and disabled when control is relinquished.

The Control Logic also has two other outputs, ANYR (Any Request) and RDD (Read Data). ANYR goes high (active) if any control requests (IOWR, etc.) are active. RDD controls the direction of the Masters Bi-directional Data Bus Drivers. The Bus Driver will always be in the Write mode (RDD = Low) except from the start of a Read Control Request to 25 to 70ns after XCP is activated.

FIGURE 2a. 8218 CONTROL LOGIC

FIGURE 2b. 8219 CONTROL LOGIC

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias    | 0°C to 70°C  |

|-----------------------------------|--------------|

| Storage Temperature65°            | °C to +150°C |

| Supply Voltage (V <sub>CC</sub> ) | -0.5V to +7V |

| Input Voltage1.0V to              | Vcc + 0.25V  |

| Output Current                    | 100mA        |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **D.C. AND OPERATING CHARACTERISTICS** $T_A = 0$ °C to 70°C; $V_{CC} = 5V \pm 5\%$

| Symbol  | Parameter                                               | Limits |      |      |      |                                                   |

|---------|---------------------------------------------------------|--------|------|------|------|---------------------------------------------------|

|         |                                                         | Min.   | Тур. | Max. | Unit | Test Conditions                                   |

| Vc      | Input Clamp Voltage                                     |        |      | -1.0 | V    | $V_{CC} = 4.75V$ , $I_{C} = -5mA$                 |

| lF      | Input Load Current MRDR/INTA/MWTR/WR IORR/RD, IOWR/IO/M |        |      | -0.5 | mA   | V <sub>CC</sub> = 5.25V<br>V <sub>F</sub> = 0.45V |

|         | Other                                                   |        |      | -0.5 | mA   |                                                   |

| lR      | Input Leakage Current                                   |        |      | 100  | μΑ   | V <sub>CC</sub> = 5.25<br>V <sub>R</sub> = 5.25   |

| VTH     | Input Threshold Voltage                                 | 0.8    |      | 2.0  | ٧.   | Vcc = 5V                                          |

| lcc     | Power Supply Current                                    |        | 200  | 240  | mA   | V <sub>CC</sub> = 5.25V                           |

| VoL     | Output Low Voltage                                      |        |      |      |      | V <sub>CC</sub> = 4.75                            |

|         | MRDC, MWTC, IORC, IOWC                                  |        |      | 0.45 | V    | I <sub>OL</sub> = 32mA                            |

|         | BREQ, BUSY                                              |        |      | 0.45 | V    | I <sub>OL</sub> = 20mA                            |

|         | XCY, RDD, ADEN                                          |        |      | 0.45 | ٧    | I <sub>OL</sub> = 16mA                            |

|         | BPRO, ANYR                                              |        |      | 0.45 | V    | $I_{OL} = 3.2 \text{mA}$                          |

| Vон     | Output High Voltage                                     |        | -    |      |      | V <sub>CC</sub> = 4.75V                           |

|         | MRDC, MWTC, IORC, IOWC<br>BUSY O.C.                     | 2.4    |      |      |      | I <sub>OH</sub> = -2mA                            |

|         | All Other Outputs                                       | 2.4    |      |      |      | $I_{OH} = -400\mu A$                              |

| los     | Short Circuit Output Current                            | 10     |      | -90  | mA   | $V_{CC} = 5.25V, V_{O} = 0V$                      |

| O (OFF) | Tri-State Output Current                                |        |      | -100 | μΑ   | $V_{CC} = 5.25V, V_O = 0.45$                      |

|         |                                                         |        |      | +100 | μΑ   | $V_{CC} = 5.25V, V_{O} = 5.25V$                   |

## A.C. CHARACTERISTICS $T_A = 0$ °C to 70°C; $V_{CC} = 5V \pm 5\%$

| C. CH  | ARACTERISTICS TA = 0°C                                       |      |        |                       |      |                               |

|--------|--------------------------------------------------------------|------|--------|-----------------------|------|-------------------------------|

| Symbol | Parameter                                                    |      | Limits | ;                     | Unit | Test Conditions               |

|        |                                                              | Min. | Тур.   | Max.                  |      |                               |

| tBCY   | Bus Clock Cycle Time                                         | 100  |        |                       | ns   | 35% to 65% Duty Cycle Charles |

| tpw    | Bus Clock Pulse Width                                        | 35   |        | 0.65 t <sub>BCY</sub> | ns   | (\$00)                        |

| tras   | RSTB to BCLK Set-Up Time                                     | 25   | 77.00  |                       | ns   |                               |

| tcss   | BCR <sub>1</sub> and BCR <sub>2</sub> to RSTB<br>Set-Up Time | 15   |        |                       | ns   |                               |

| tcsн   | BCR <sub>1</sub> and BCR <sub>2</sub> to RSTB<br>Hold Time   | 15   |        |                       | ns   |                               |

| tRQD   | BCLK to BREQ Delay                                           |      |        | 35                    | ns   |                               |

| tprns  | BPRN to BCLK Set-Up Time                                     | 23   |        |                       | ns   |                               |

| tBNO   | BRPN to BPRO Delay                                           |      |        | 30                    | ns   |                               |

| tBYD   | BCLK to BUSY Delay                                           |      |        | 55                    | ns   |                               |

| tCAD   | MRDR, MWTR, IORR, IOWR to ANYR Delay                         |      |        | 30                    | ns   |                               |

| tsxD   | XSTR to XCY Delay                                            |      |        | 40                    | ns   |                               |

| tsco   | XSTR to MRDC, MWTC, IORC, IOWC Delay                         | 50   | ***    | 200                   | ns   | Adjustable by External R/C    |

| txsw   | XSTR Pulse Width                                             | 30   |        |                       | ns   |                               |

| txcd   | XCP to MRDC, MWTC, IORC, IOWC Delay                          |      |        | 50                    | ns   |                               |

| txcw   | XCP Pulse Width                                              | 35   |        |                       | ns   |                               |

| tccp   | XCP to XCY Delay                                             | 50   |        | 200                   | ns   | Adjustable by External R/C    |

| tcmd   | MRDR, MWTR, IORR, IOWR<br>to MRDC, MWTC, IORC, IOWC          |      |        | 35                    | ns   |                               |

| tCRD   | MRDR, MWTR, IORR, IOWR to RDD Delay                          |      |        | 25                    | ns   |                               |

| trw    | RSTB Min. Neg. Pulse Width                                   | 30   |        |                       | ns   |                               |

| tCPD   | BCLK to BPRO Delay                                           |      |        | 40                    | ns   |                               |

| txRD   | XCP to RDD Delay                                             | 25   |        | 70                    | ns   |                               |

## 8218/19 XSTR TO OUTPUT COMMAND DELAY ONESHOT DELAY VS. DELAY ADJUST CAPACITANCE AND RESISTANCE

6-96

FIGURE 3b. 8218/8219 CONTROL CYCLE (SYSTEM BUS PREVIOUSLY NOT IN USE).

FIGURE 3c. 8218/8219 BUS CONTROL EXCHANGE (MASTER NO. 1 LEAVING BUS AND MASTER NO. 2 GETTING ON BUS).

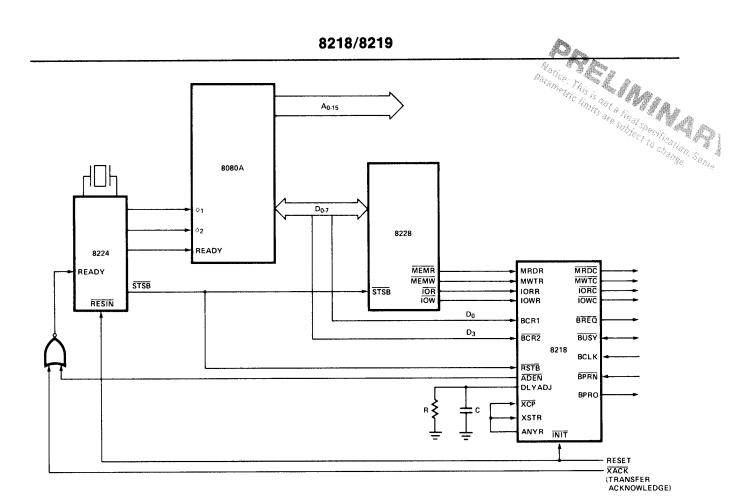

FIGURE 4a. MCS-80 CPU WITH 8218.

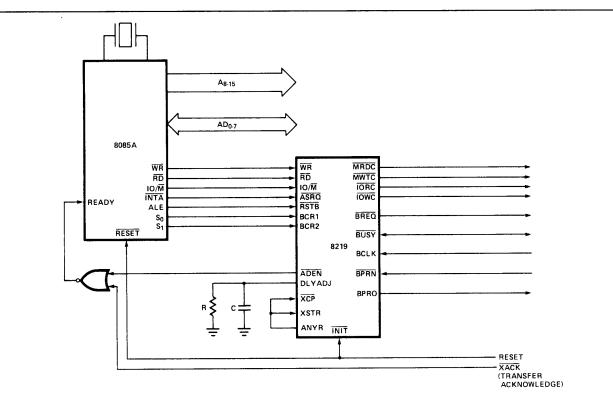

FIGURE 4b. MCS-85 CPU WITH 8219.

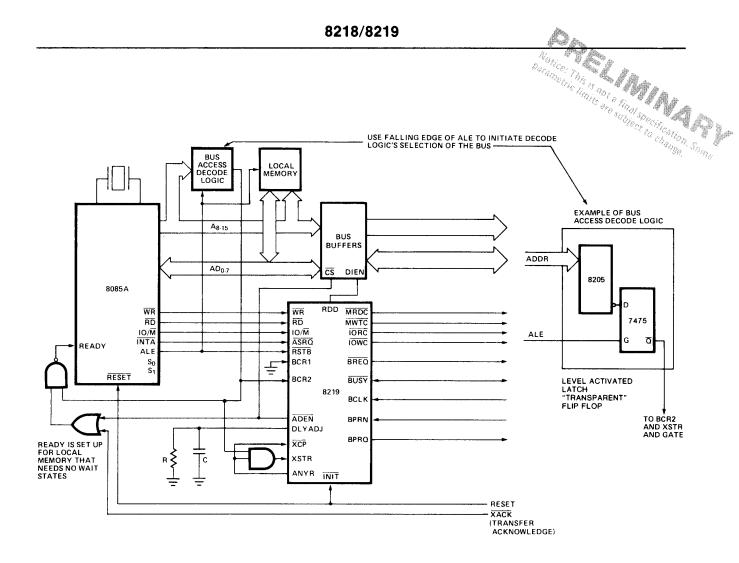

FIGURE 4c. MCS-85 CPU WITH 8219 USING LOCAL MEMORY.

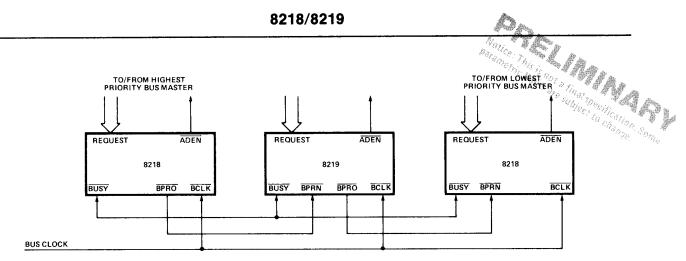

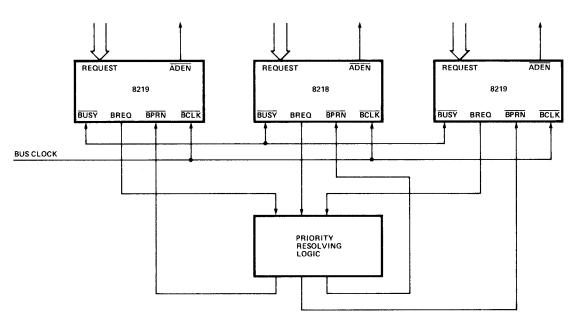

"DAISY CHAIN" CONFIGURATION

PARALLEL REQUEST CONFIGURATION

FIGURE 5. TWO METHODS OF CONNECTING MULTIPLE 8218/8219's TO RESOLVE BUS CONTENTION AMONG MULTIPLE MASTERS.