Nchವ

свзДа

D2728, APRIL 1983, REVISED DECEMBER 1983

80 Vcc

률[]SEF

so

6 6 6

NC-No internal connection.

| <ul> <li>Detects and Corrects Single-Bit Errors</li> <li>Detects and Flags Dual-Bit Errors</li> <li>Fast Processing Times:<br/>Write Cycle: Generates Check Word in<br/>45 ns Typical<br/>Read Cycle: Flags Errors in 27 ns<br/>Typical</li> <li>Power Dissipation 500 mW Typical</li> <li>Choice of Output Configurations:<br/>'LS6363-State<br/>'LS637 Open Collector</li> </ul> | SN54LS' J PACKAGE<br>SN74LS' DW, J OR N PACKAGE<br>(TOP VIEW)<br>DEF 1 20 VCC<br>DB0 2 19 SEF<br>DB1 3 18 S1<br>DB2 4 17 S0<br>DB3 5 16 CB0<br>DB4 6 15 CB1<br>DB5 7 14 CB2<br>DB6 8 13 CB3<br>DB7 9 12 NC<br>GND 10 11 CB4 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                    | SN54LS' FK PACKAGE<br>SN74LS' FN PACKAGE<br>(TOP VIEW)                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                    | DB7 2 0 5 4                                                                                                                                                                                                                 |

| description                                                                                                                                                                                                                                                                                                                                                                        | (ဂ)ဖြ မျှံစြB1                                                                                                                                                                                                              |

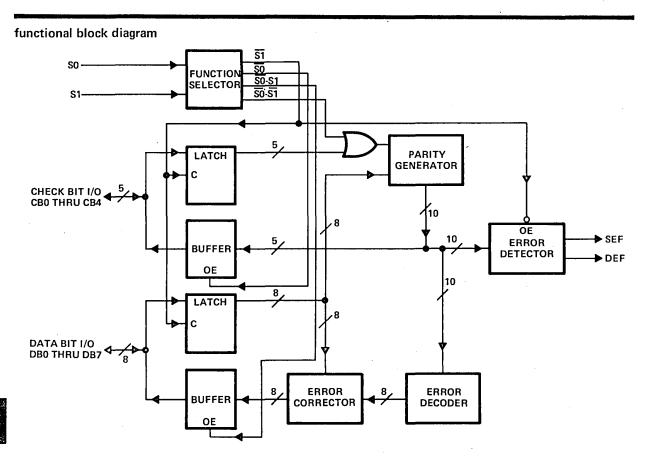

| The 'LS636 and 'LS637 devices are 8-bit parallel error detection and correction circuits (EDACs) in 20-pin,                                                                                                                                                                                                                                                                        | ₩13 ~ DBO                                                                                                                                                                                                                   |

detection and correction circuits (EDACs) in 20-pin, 300-mil packages. They use a modified Hamming code to generate a 5-bit check word from an 8-bit data word. This check word is stored along with the data word during the memory write cycle. During the memory read cycle, the 13-bit words from memory are processed by the EDACs to determine if errors have occurred in memory.

Single-bit errors in the 8-bit data word are flagged and corrected.

- Single-bit errors in the 5-bit check word are flagged, and the CPU sends the EDAC through the correction cycle even though the 8-bit word is not in error. The correction cycle will simply pass along the original 8-bit word in this case and produce error syndrome bits to pinpoint the error-generating location.

- Dual-bit errors are flagged but not corrected. These dual errors may occur in any two bits of the 13-bit word from memory (two errors in the 8-bit data word, two errors in the 5-bit check word, or one error in each word).

The gross-error condition of all highs from memory will be detected. Otherwise, errors in three or more bits of the 13-bit word are beyond the capabilities of these devices to detect.

| MEMORY | CONTROL |    |                                               |                       |                      | ERROR FLAGS |      |  |

|--------|---------|----|-----------------------------------------------|-----------------------|----------------------|-------------|------|--|

| CYCLE  | S1      | SO | EDAC FUNCTION                                 | DATA I/O              | CHECK WORD I/O       | SEF         | DEF  |  |

| WRITE  | L       | L  | Generate Check Word                           | Input Data            | Output Check Word    | L           | L    |  |

| READ   | L       | Н  | Read Data & Check Word                        | Input Data            | Input Check Word     | LL          |      |  |

| READ   | Н       | н  | Latch & Flag Errors                           | Latch Data            | Latch Check Word     | Ena         | bled |  |

| READ   | н       | L  | Correct Data Word &<br>Generate Syndrome Bits | Output Corrected Data | Output Syndrome Bits | Ena         | bled |  |

#### CONTROL FUNCTION TABLE

PRODUCTION DATA This document contains information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

**ITL DEVICES**

#### ERROR FUNCTION TABLE

| TOTAL NU   | JMBER OF ERRORS | ERROF | R FLAGS | DATA           |

|------------|-----------------|-------|---------|----------------|

| 8-BIT DATA | 5-BIT CHECKWORD | SEF   | DEF     | CORRECTION     |

| 0          | 0               | L     | L       | Not Applicable |

| 1          | 0               | н     | L       | Correction     |

| 0          | 1               | н     | L       | Correction     |

| 1          | 1               | н     | н       | Interrupt      |

| 2          | · 0             | н     | н       | Interrupt      |

| 0          | 2               | н     | н       | Interrupt      |

In order to be able to determine whether the data from the memory is acceptable to use as presented to the bus, the EDAC must be strobed to enable the error flags and the flags will have to be tested for the zero condition.

The first case in the error function table represents the normal, no-error condition. The CPU sees lows on both flags. The next two cases of single-bit errors require data correction. Although the EDAC can discern the single check bit error and ignore it, the error flags are identical to the single error in the 8-bit data word. The CPU will ask for data correction in both cases. An interrupt condition to the CPU results in each of the last three cases, where dual errors occur.

#### error detection and correction details

During a memory write cycle, five check bits (CB0-CB4) are generated by eight-input parity generators using the data bits as defined below. During a memory read cycle, the 5-bit check word is retrieved along with the 8-bit data word.

TTL DEVICES

3-1222

| CHECKWORD |   |   |   | 8-BIT DA | TA WORD | ) |   |   |

|-----------|---|---|---|----------|---------|---|---|---|

| BIT       | 0 | 1 | 2 | 3        | 4       | 5 | 6 | 7 |

| CB0       | X | X |   | X        | X       |   |   |   |

| CB1       | x |   | х | х        |         | х | х |   |

| CB2       |   | х | х |          | Χ.      | х |   | х |

| CB3       | x | х | х |          |         |   | x | х |

| CB4       |   |   |   | х        | х       | х | х | х |

The five check bits are parity bits derived from the matrix of data bits as indicated by "X" for each bit.

Error detection is accomplished as the 5-bit check word and the 8-bit data word from memory are applied to internal parity generators/checkers. If the parity of all five groupings of data and check bits are correct, it is assumed that no error has occurred and both error flags will be low.

If the parity of one or more of the check groups is incorrect, an error has occurred and the proper error flag or flags will be set high. Any single error in the 8-bit data word will change the sense of exactly three bits of the 5-bit check word. Any single error in the 5-bit check word changes the sense of only that one bit. In either case, the single error flag will be set high while the dual error flag will remain low.

Any two-bit error will change the sense of an even number of check bits. The two-bit error is not correctable since the parity tree can only identify single-bit errors. Both error flags are set high when any two-bit error is detected.

Three or more simultaneous bit errors can fool the EDAC into believing that no error, a correctable error, or an uncorrectable error has occurred and produce erroneous results in all three cases.

Error correction is accomplished by identifying the bad bit and inverting it. Identification of the erroneous bit is achieved by comparing the 8-bit data word and 5-bit check word from memory with the new check word with one (check word error) or three (data word error) inverted bits.

As the corrected word is made available on the data word I/O port, the check word I/O port presents a 5-bit syndrome error code. This syndrome code can be used to identify the bad memory chip.

| ERROR LOCATION | 1    | SYND | ROME ERROP | CODE |     |

|----------------|------|------|------------|------|-----|

| ENNOR LOCATION | СВО  | CB1  | CB2        | CB3  | CB4 |

| DBO            | L    | L    | H          | L    | Н   |

| DB1            | L    | н    | L          | L    | н   |

| DB2            | н    | L    | L          | L    | ́ Н |

| DB3            | L    | L    | н          | н    | L   |

| DB4            | / L  | н    | L          | н    | L   |

| DB5            | н    | L    | L          | н    | L   |

| DB6            | н    | L    | н          | L    | L   |

| DB7            | н    | н    | L          | L,   | L   |

| CB0            | {· ι | Η.   | н          | · H  | · H |

| CB1            | н    | L    | н          | н    | н   |

| CB2            | н.   | н    | L          | н    | н   |

| CB3            | н    | н    | н          | L    | н   |

| CB4            | н    | н    | н          | н    | L   |

| NO ERROR       | н    | н    | н          | н    | н   |

#### ERROR SYNDROME TABLE

TL DEVICES

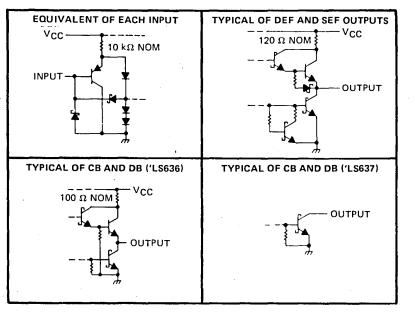

### schematics of inputs and outputs

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|   | Supply voltage, V <sub>CC</sub> (see Note 1)               | 7 V      |

|---|------------------------------------------------------------|----------|

|   | Input voltage: S0 and S1                                   | 7 V      |

| ÷ | CB and DB                                                  | 5.5 V    |

|   | Off-state output voltage                                   | 5.5 V    |

|   | Operating free-air temperature range: SN54LS636, SN54LS637 | 5 125° C |

|   | SN74LS636, SN74LS637                                       | to 70°C  |

|   | Storage temperature range                                  | o 150° C |

NOTE 1: Voltage values are with respect to network ground terminal.

### recommended operating conditions

|                 |                                |                                       | _   | 36<br>37 | SI<br>SI | UNIT |     |      |      |  |

|-----------------|--------------------------------|---------------------------------------|-----|----------|----------|------|-----|------|------|--|

|                 | <u> </u>                       |                                       | MIN | NOM      | MAX      | MIN  | NOM | MAX  |      |  |

| Vcc             | Supply voltage                 |                                       | 4.5 | 5        | 5.5      | 4.75 | 5   | 5.25 | v    |  |

| 1               | High-level output current      | CB or DB, 'LS636 only                 |     |          | 1        |      |     | -1   | - mA |  |

| юн              |                                | DEF or SEF                            |     |          | -0.4     |      |     | -0.4 |      |  |

| Voн             | High-level output voltage      | CB or DB, 'LS637 only                 |     |          | 5.5      |      |     | 5.5  | V    |  |

|                 | Low-level output current       | CB or DB                              |     |          | 12       |      |     | 24   |      |  |

| IOL             | Low-level output current       | DEF or SEF                            |     |          | 4        |      |     | 8    | mA   |  |

| •               | Setup time                     | CB or DB before S111                  | 15  |          |          | 15   |     |      |      |  |

| t <sub>su</sub> | Setup time                     | CB or DB before S11‡                  | 45  |          |          | . 45 |     |      | ns   |  |

| th              | Hold time                      | CB or DB after S1 t                   | 15  |          |          | 15   |     |      | ns   |  |

| TA              | Operating free-air temperature | · · · · · · · · · · · · · · · · · · · | -55 |          | 125      | 0    |     | 70   | °C   |  |

† This time guarantees the input data and checkword will be latched.

This time guarantees the input data and checkword will be latched plus that no glitch will occur on SEF or DEF flags.

† The upward-pointing arrow indicates a transition from low to high.

3

**TTL DEVICES**

|                  | ······································                  |            |                                                                 | · · · · · · · · · · · · · · · · · · · | SN  | 154 L Se | 36   | s   | N74LS | 636   |      |

|------------------|---------------------------------------------------------|------------|-----------------------------------------------------------------|---------------------------------------|-----|----------|------|-----|-------|-------|------|

|                  | PARAMETERS                                              |            | TEST CON                                                        | DITIONS <sup>†</sup>                  | MIN | түр‡     | MAX  | MIN | түр‡  | MAX   | UNIT |

| VIH              | High-level input voltage                                |            |                                                                 |                                       | 2   |          |      | 2   |       |       | V    |

| VIL              | Low-level input voltage                                 |            |                                                                 |                                       |     |          | 0.7  |     |       | 0.8   | V    |

| VIK              | Input clamp voltage                                     |            | V <sub>CC</sub> = MIN,                                          | l <sub>l</sub> =18 mA                 |     |          | -1.5 |     |       | -1.5  | V    |

| ∨он              | High-level output voltage                               | CB or DB   | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = 2 V,                | I <sub>OH</sub> = MAX                 | 2.4 | 3.3      |      | 2.4 | 3.2   |       | v    |

| VOH              |                                                         | DEF or SEF | $V_{1L} = V_{1L} min$                                           | I <sub>OH</sub> =400 μA               | 2.5 | 3.4      |      | 2.7 | 3.4   |       |      |

|                  |                                                         | CB or DB   | Vcc = MIN,                                                      | I <sub>OL</sub> = 12 mA               |     | 0.25     | 0.4  |     | 0.25  | 0.4   |      |

| VOL              | Low-level output voltage                                |            | $V_{1H} = 2 V,$                                                 | l <sub>OL</sub> = 24 mA               |     |          |      |     | 0.35  | 0.5   | v    |

| ·UL              |                                                         | DEE or SEE | VIL = VIL max                                                   | $I_{OL} = 4 \text{ mA}$               |     | 0.25     | 0.4  |     | 0.25  | 0.4   |      |

|                  |                                                         |            |                                                                 | IOL = 8 mA                            |     |          |      |     | 0.35  | i 0.5 |      |

| юzн              | Off-state output current,<br>high-level voltage applied | CB or DB   | V <sub>CC</sub> = MAX,<br>S0 and S1 at 2 V                      | V <sub>O</sub> = 2.7 V,               |     |          | 20   |     |       | 20    | μA   |

| <sup>1</sup> OZL | Off-state output current,<br>low-level voltage applied  | CB or DB   | V <sub>CC</sub> = MAX,<br>S0 and S1 at 2 V                      | V <sub>O</sub> = 0.4 V,               |     | -        | -0.2 |     |       | -0.2  | mA   |

|                  | Input current at maximum                                | CB or DB   | V <sub>CC</sub> = MAX,                                          | VI = 5.5 V                            | [   |          | 0.1  |     |       | 0.1   | mA   |

| '1               | input voltage                                           | S0 or S1   | V <sub>IH</sub> = 4.5 V                                         | V1 = 7 V                              | 1   |          | 0.1  |     |       | 0.1   |      |

| ΪН               | High-level input current                                |            | V <sub>CC</sub> = MAX,                                          | VI = 2.7 V                            | 1   |          | 20   |     |       | 20    | μA   |

| hί               | Low-level input current                                 |            | V <sub>CC</sub> = MAX,                                          | V <sub>I</sub> = 0.4 V                |     |          | -0.2 |     |       | -0.2  | mA   |

| los§             | Short-circuit output                                    | CB or DB   | V <sub>CC</sub> = MAX                                           | <u> </u>                              |     |          | -130 | -30 |       | -130  | mA   |

| .05.8            | current                                                 | DEF or SEF |                                                                 |                                       | -20 |          | -100 | -20 |       | -100  |      |

| lcc              | Supply current                                          | -          | V <sub>CC</sub> = MAX, S0<br>All CB and DB pi<br>DEF and SEF op | ns grounded,                          |     | 100      | 160  |     | 100   | 160   | mA   |

| electrical characteristics over recommended o | perating | free-air tem | perature range | (unless otherwise noted) |

|-----------------------------------------------|----------|--------------|----------------|--------------------------|

|                                               | P0101113 |              |                | (                        |

|                | PARAMETER                              | ······································                   | TECT CO                                                             |                                                                     | SI       | 154LS6 | 37   | s        | N74LS            | 637        |      |

|----------------|----------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------|--------|------|----------|------------------|------------|------|

|                | TANAWETEN                              |                                                          | TEST CON                                                            |                                                                     | MIN      | TYP‡   | MAX  | MIN      | TYP <sup>‡</sup> | MAX        | UNIT |

| VIH            | High-level input voltage               |                                                          |                                                                     |                                                                     | 2        |        |      | 2        |                  |            | v    |

| VIL            | Low-level input voltage                |                                                          |                                                                     |                                                                     |          |        | 0.7  |          |                  | 0.8        | V    |

| VIK            | Input clamp voltage                    |                                                          | V <sub>CC</sub> = MIN,                                              | l <sub>l</sub> = –18 mA                                             |          |        | -1.5 |          |                  | -1.5       | v    |

| ∨он            | High-level output voltage              | DEF or SEF                                               | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = 2 V,                    | I <sub>OH</sub> = -400 μA,<br>V <sub>IL</sub> = V <sub>IL</sub> max | 2.5      | 3.4    |      | 2.7      | 3.4              |            | v    |

| юн             | High-level output current              | CB or DB                                                 | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = 2 V,                    | V <sub>OH</sub> = 5.5 V,<br>V <sub>IL</sub> = V <sub>IL</sub> max   |          |        | 0.1  |          |                  | 0.1        | mA   |

|                |                                        | _ow-level output voltage CB or DB V <sub>CC</sub> = MIN, |                                                                     | I <sub>OL</sub> = 12 mA                                             |          | 0.25   | 0.4  | <u> </u> | 0.25<br>0.35     | 0.4<br>0.5 |      |

| VOL            | Low-level output voltage               | DEF or SEF                                               |                                                                     | 1 <sub>OL</sub> = 4 mA<br>1 <sub>OL</sub> = 8 mA                    |          | 0.25   | 0.4  |          | 0.25             | 0.4<br>0.5 | V    |

| ۱ <sub>I</sub> | Input current at maximum input voltage | CB or DB<br>S0 or S1                                     | V <sub>CC</sub> = MAX,<br>V <sub>IH</sub> = 4.5 V                   | V <sub>I</sub> = 5.5 V<br>V <sub>I</sub> = 7 V                      |          |        | 0.1  |          |                  | 0.1        | mA   |

| Чн             | High-level input current               | •                                                        | V <sub>CC</sub> = MAX                                               | V <sub>1</sub> = 2.7 V                                              | [        |        | 20   |          |                  | 20         | μA   |

| 4L             | Low-level input current                | ······································                   | V <sub>CC</sub> = MAX,                                              | V   = 0.4 V                                                         | <u> </u> |        | -0.2 |          |                  | -0.2       | mA   |

| IOS§           | Short-circuit output<br>current        | DEF or SEF                                               | V <sub>CC</sub> = MAX                                               |                                                                     | -20      |        | -100 | -20      |                  | -100       | mA   |

| Icc            | Supply current                         |                                                          | V <sub>CC</sub> = MAX, S0 a<br>All CB and DB gro<br>SEF and DEF ope | ounded,                                                             |          | 90     | 144  |          | 90               | 144        | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

\$Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

TTL DEVICES

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FROM    | то       | TEST CONDITIONS                   |     | 'LS63 | 6   | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-----------------------------------|-----|-------|-----|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (INPUT) | (OUTPUT) | TEST CONDITIONS                   | MIN | TYP   | MAX | ONIT |

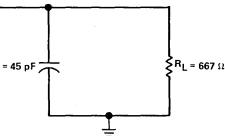

| tPLH Propagation delay time, low-to-high-level output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DB      | СВ       | S0 at 0 V, S1 at 0 V,             |     | 31    | 45  | ns   |

| tPHL Propagation delay time, high-to-low-level output <sup>o</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UB      |          | $R_L = 667 \Omega$ , See Figure 1 |     | 45    | 65  | ns   |

| tpj H Propagation delay time, low-to-high-level output*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | DEF      | S0 at 3 V, $R_L = 2 k\Omega$ ,    |     | 27    | 40  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S1†     | SEF      | See Figure 1                      |     | 20    | 30  | ns   |

| tpzH Output enable time to high level#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S01     | CB, DB   | S1 at 3 V, $R_L = 667 \Omega$ ,   |     | 24    | 40  | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |          | See Figure 2                      |     |       |     | 113  |

| tpz1 Output enable time to low level#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | S0↓     | CB, DB   | S1 at 3 V, $R_L = 667 \Omega$ ,   |     | 30    | 45  | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00+     | 00,00    | See Figure 1                      |     |       | 45  | 115  |

| tpH7 Output disable time from high level <sup>▲</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SOT     | CB, DB   | S1 at 3 V, $R_L = 667 \Omega$ ,   |     | 43    | 65  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 501     | CB, DB   | See Figure 2                      | 4.  |       | 05  | ns   |

| tp17 Output disable time from low level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s0+     | CP DP    | S1 at 3 V, $R_L = 667 \Omega$     | ,   | 31    | 45  |      |

| the source of the second s | S0†     | CB, DB   | See Figure 1                      |     | 31    | 45  | ns   |

## 'LS636 switching characteristics, $V_{CC} = 5 V$ , $T_A = 25 °C$ , $C_L = 45 pF$

## 'LS637 switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C, C<sub>L</sub> = 45 pF, see Figure 1

| PARAMETER                                                          | FROM    | то       | TEST CONDITIONS              |     | 'LS637 |     |      |  |

|--------------------------------------------------------------------|---------|----------|------------------------------|-----|--------|-----|------|--|

|                                                                    | (INPUT) | (OUTPUT) | TEST CONDITIONS              | MIN | ТҮР    | MAX | UNIT |  |

| tpLH Propagation delay time, low-to-high level output <sup>♦</sup> | DB      | СВ       | S0 at 0 V, S1 at 0V,         |     | 38     | 55  | ns   |  |

| tPHL Propagation delay time, high-to-low-level output <sup>o</sup> |         |          | RL = 667 Ω                   |     | 45     | 65  | ns   |  |

| TPLH Propagation delay time, low-to-high-level output*             | S1†     | DEF      | S0 at 3 V, $R_1 = 2 k\Omega$ |     | 27     | 40  | ns   |  |

|                                                                    | 511     | SEF      | 50 at 5 V, h[ - 2 k32        |     | 20     | 30  | ns   |  |

| tPHL Propagation delay time, high-to-low-level output#             | S01     | CB, DB   | S1 at 3 V, RL = 667 ks       | 2   | 28     | 45  | ns   |  |

| tPLH Propagation delay time, low-to-high-level output              | SOT     | CB, DB   | S1 at 3 V, RL = 667 ks       | 2   | 33     | 50  | ns   |  |

<sup>O</sup>These parameters describe the time intervals taken to generate the check word during the memory write cycle.

$^{\star}$ These parameters describe the time intervals taken to flag errors during the memory read cycle.

<sup>#</sup>These parameters describe the time intervals taken to correct and output the data word and to generate and output the syndrome error code during the memory read cycle.

These parameters describe the time intervals taken to disable the CB and DB buses in preparation for a new data word during the memory read cycle.

## PARAMETER MEASUREMENT INFORMATION

$V_{CC} = 5 V \qquad OUTPUT \\ OF CIRCUIT O \\ = C_L = 45 pF \qquad C_L = 45 pF$

FIGURE 1-OUTPUT LOAD CIRCUIT

FIGURE 2-OUTPUT LOAD CIRCUIT

typical operating sequences READ, FLAG, AND CORRECT MODE SWITCHING WAVEFORMS S0 S1 · t<sub>su</sub>t •thold 🗕 INPUT DATA WORD DB0-DB7 OUTPUT CORRECTED DATAWORD tdie thold tsu CBO-CB4 INPUT CHECK WORD OUTPUT SYNDROME CODE M tdis **→** t<sub>en</sub> tpd VALID SEF FLAG SEF tpd VALID DEF FLAG DEF

<sup>†</sup> NOTE: There are two conditions specified for t<sub>su</sub> of Data or Checkword before S1<sup>†</sup>. See recommended operating conditions for detail.

TEXAS INSTRUMENTS POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

<u>3</u>-1227