SN54120 ... J OR W PACKAGE

SN74120 ... J OR N PACKAGE

(TOP VIEW)

15**[**]2M

14 2 S2

13 2<del>5</del>1

11 🗌 2C

10 2 Y

9 🗌 2 Y

12 2 Z R

15102

1<u>5</u>2[]3

1R[]4

1C∏5

1Y∏6

1¥[]7

ß

**GND**

SEPTEMBER 1971-REVISED DECEMBER 1983

- Generates Either a Single Pulse or Train of Pulses Synchronized with Control Functions

- Ideal for Implementing Sync-Control Circuits

Similar to those Used in Oscilloscopes

- Latched Operation Ensures that Output Pulses Are Not Clipped

- High-Fan-Out Complementary Outputs Drive System Clock Lines Directly

- Internal Input Pull-Up Resistors Eliminate

Need for External Components

- Diode-Clamped Inputs Simplify System Design

- Typical Propagation Delays:

9 Nanoseconds through One Level 16 Nanoseconds through Two Levels

### description

These monolithic pulse synchronizers are designed to synchronize an asynchronous or manual signal with a system clock. Reliable response is ensured as the input signals are latched up; therefore duration of logic input is not critical and the adverse effects of contact-bounce of a manual input are eliminated. The ability to pass output pulses is started and stopped by the levels or pulses applied to the latch inputs  $\overline{S1}$ ,  $\overline{S2}$ , or  $\overline{R}$  in accordance with the function table. High-speed circuitry is utilized throughout the clock paths to minimize skew with respect to the system clock.

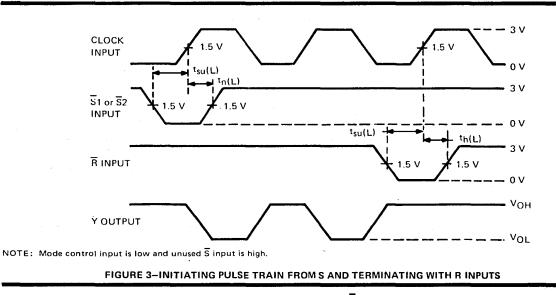

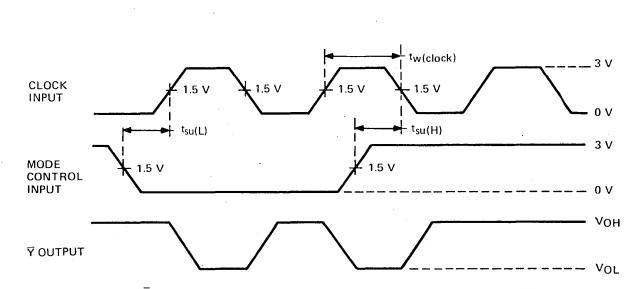

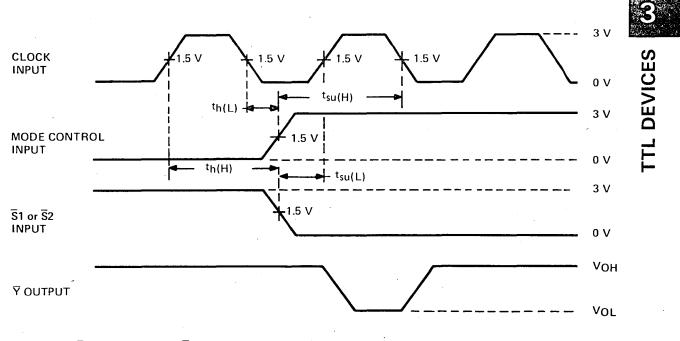

After initiation, the mode control (M) input determines whether a series of pulses or only one pulse is passed. In the absence of a stop command, the clock driver will continue to pass clock pulses as long as the mode control input is low (see Figures 2 through 4). If the mode control input is high only a single clock pulse will be passed (see Figure 5).

When the mode control is set to pass a series of pulses, the last pulse out is determined by two general rules:

a. When pulses are terminated by the S or R inputs, conditions meeting the setup times (specified under recommended operating conditions) will dominate.

|   | FUNCTION TABLE |             |            |                       |  |  |  |  |  |  |  |  |

|---|----------------|-------------|------------|-----------------------|--|--|--|--|--|--|--|--|

| 1 |                | INPUTS      | S          | FUNCTION              |  |  |  |  |  |  |  |  |

|   | R              | <u></u> \$1 | <b>S</b> 2 | FUNCTION              |  |  |  |  |  |  |  |  |

|   | Х              | L           | х          | Pass Output Pulses    |  |  |  |  |  |  |  |  |

|   | х              | х           | L          | Pass Output Pulses    |  |  |  |  |  |  |  |  |

|   | L              | н           | н          | Inhibit Output Pulses |  |  |  |  |  |  |  |  |

|   | н              | Ļ           | н          | Start Output Pulses   |  |  |  |  |  |  |  |  |

|   | н              | н           | Ļ          | Start Output Pulses   |  |  |  |  |  |  |  |  |

|   | ţ              | н           | н          | Stop Output Pulses    |  |  |  |  |  |  |  |  |

|   | н              | н           | н          | Continue <sup>†</sup> |  |  |  |  |  |  |  |  |

H = high level (steady state)

- L = low level (steady state)

- $\downarrow$  = transition from H to L

- X = irrelevant

<sup>†</sup>Operation initiated by last  $\downarrow$  transition continues.

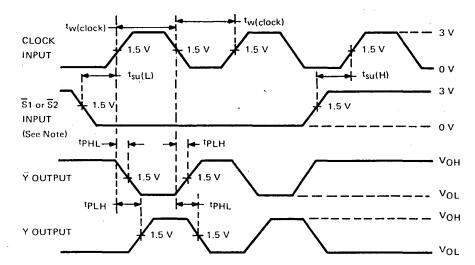

b. Low-to-high-level transitions at the mode control input should be avoided during the 20-nanosecond period immediately following the negative transition of the input clock pulse as transitions during this time period may or may not allow the next pulse to pass (see Figures 4 and 5). When pulses are terminated by the mode control input, a positive transition at the mode control input meeting the high-level setup time, t<sub>su</sub> (H), (specified under recommended operating conditions) will pass that positive clock pulse then inhibit remaining clock pulses. The clock input (C) is latch-controlled ensuring that once initiated the output pulse will not be terminated until the full pulse has been passed.

PRODUCTION DATA This document contains information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TL DEVICES

### description (continued)

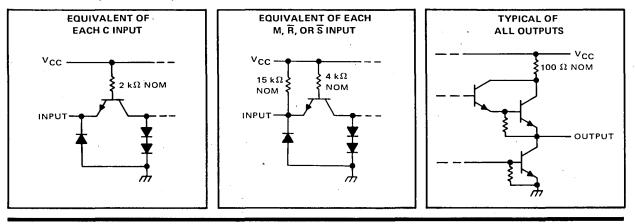

This clock driver circuit is entirely compatible for use with either digital logic circuits or mechanical switches for input controls since all inputs, except the clock, have internal pull-up resistors. This eliminates the requirement to supply an external resistor to prevent the input from floating when the control switch is open. The internal resistor also means that these inputs may be left disconnected if unused.

Typical propagation delay time is 9 nanoseconds to the  $\overline{Y}$  output and 16 nanoseconds to the Y output from the clock input. The outputs will drive 60 Series 54/74 loads at a high logic level and 30 loads at a low logic level. Typical power dissipation is 127 milliwatts per driver. The SN54120 is characterized for operation from -55°C to 125°C; the SN74120 is characterized for operation from 0°C to 70°C.

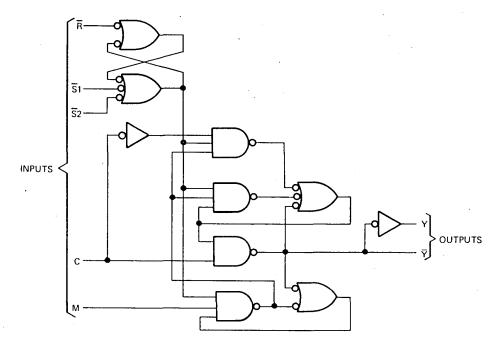

### logic diagram (each driver)

3

### schematics of inputs and outputs

TEXAS TEXAS TEXAS TEXAS 75265

3-466

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1) .    | • |    |     |     |      |     |     |   |  |   |  | • |   |   |  |  | • |   |   |  |   |     |    |     | 7 V    |

|---------------------------------------|---|----|-----|-----|------|-----|-----|---|--|---|--|---|---|---|--|--|---|---|---|--|---|-----|----|-----|--------|

| Input voltage                         |   |    |     |     |      |     |     |   |  | • |  |   |   |   |  |  |   |   |   |  |   |     |    |     | 5.5 V  |

| Interemitter voltage (see Note 2) .   |   |    |     |     |      |     |     |   |  |   |  |   |   |   |  |  |   |   |   |  |   |     |    |     | 5.5 V  |

| Operating free-air temperature range: | S | NE | 541 | 120 | ) Ci | irc | uit | s |  |   |  |   |   | • |  |  |   | • |   |  | - | -55 | °C | to  | 125°C  |

|                                       | S | N7 | 741 | 120 | ) Ci | irc | uit | s |  |   |  |   |   |   |  |  |   |   |   |  |   |     | 0° | C t | o 70°C |

| Storage temperature range             |   |    |     | •   |      |     |     |   |  |   |  |   | - |   |  |  |   |   | • |  |   | 65  | °C | to  | 150°C  |

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter transistor. For this circuit, this rating applies between the S1 and S2 inputs.

#### recommended operating conditions

|                                                | · · · · · · · · · · · · · · · · · · ·                    |                     |     | SN5412 | 0    |      |     |                                |      |

|------------------------------------------------|----------------------------------------------------------|---------------------|-----|--------|------|------|-----|--------------------------------|------|

|                                                |                                                          |                     | MIN | NOM    | MAX  | MIN  | NOM | 0<br>MAX<br>5.25<br>-2.4<br>48 | UNIT |

| Supply voltage, V <sub>CC</sub>                |                                                          |                     | 4.5 | 5      | 5.5  | 4.75 | 5   | 5.25                           | V    |

| High-level output current, IOH                 |                                                          |                     |     |        | -2.4 |      |     | -2.4                           | mA   |

| Low-level output current, IOL                  |                                                          |                     |     |        | 48   |      |     | 48                             | mA   |

|                                                | Any input exc<br>t <sub>su</sub> (H or L)                | ept mode control,   | 12  |        |      | 12   |     |                                |      |

| Setup time (see Figures 2 thru 5) Mode control |                                                          |                     |     |        |      | 0    |     |                                | ns   |

|                                                | Mode control                                             | t <sub>su</sub> (L) | 12  |        |      | 12   |     |                                |      |

| Hold time (see Figures 3 and 5)                | Any input excer<br>gures 3 and 5) <sup>t</sup> h(H or L) |                     | 3   |        |      | 3    |     |                                | ns   |

|                                                | Mode control,                                            | th(H or L)          | 20  |        |      | 20   |     |                                | 1    |

| Operating free-air temperature, TA             | -55                                                      |                     | 125 | 0      |      | 70   | °C  |                                |      |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                              |              | TEST CC                                            | NDITIONS <sup>†</sup>                               | MIN   | TYP‡ | MAX   | רואט |

|-----|----------------------------------------|--------------|----------------------------------------------------|-----------------------------------------------------|-------|------|-------|------|

| VIH | High-level input voltage               |              |                                                    |                                                     | 2     |      |       | ۰v   |

| VIL | Low-level input voltage                |              |                                                    |                                                     | 1     |      | 0.8   | V    |

| VIK | Input clamp voltage                    |              | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = -12 mA                             |       |      | -1.5  | V    |

| Vон | High-level output voltage              |              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -2.4 mA | 2.4   | 3.4  |       | v    |

| VOL | Low-level output voltage               |              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 48 mA   |       | 0.2  | 0.4   | v    |

| -lj | Input current at maximum input voltage |              | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                              | 1     |      | 1     | mA   |

|     |                                        | Clock input  |                                                    | <u> </u>                                            |       |      | 80    | μA   |

| ЧН  | High-level input current               | Other inputs | V <sub>CC</sub> = MAX,                             | VI = 2.4 V                                          | -0.12 | -0.2 | -0.36 | mA   |

|     |                                        | Clock input  |                                                    |                                                     |       |      | -3.2  |      |

| ΠL  | Low-level input current                | Other inputs | V <sub>CC</sub> = MAX,                             | v <sub>1</sub> = 0.4 v                              |       |      | -2.1  | MA   |

| los | Short-circuit output current §         |              | V <sub>CC</sub> = MAX                              |                                                     | -35   |      | -90   | mA   |

| 100 | Supply current                         | •            | V <sub>CC</sub> = MAX,                             | See Note 3                                          |       | 51   | 90    | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. <sup>§</sup>Not more than one output should be shorted at a time. NOTE 3: I<sub>CC</sub> is measured with ground applied to all inputs except R which is at 4.5 V and all outputs open.

### switching characteristics, $V_{CC} = 5 V$ , $T_{A} = 25^{\circ}C$

| PARAMETER¶             | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                           | MIN | түр         | МАХ | רואט |

|------------------------|-----------------|----------------|-------------------------------------------|-----|-------------|-----|------|

| <sup>t</sup> PLH       | <u> </u>        | V              | 0 - 15 - 5                                |     | 14          | 22  |      |

| <sup>t</sup> PHL       | U U             | T T            | $C_{L} = 45  \text{pF},$                  |     | <u>`</u> 17 | 25  | ns   |

| <sup>Ф</sup> LН<br>ФНL | <u> </u>        |                | - R <sub>L</sub> = 133 Ω,<br>See Figure 1 |     | 10          | 16  |      |

|                        | C               |                | See Figure 1                              |     | 8           | 13  | ns   |

¶tPLH # Propagation delay time, low-to-high-level output tpHL = Propagation delay time, high-to-low-level output

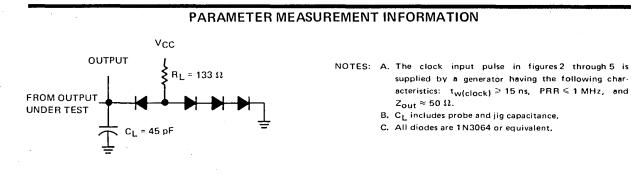

FIGURE 1-LOAD CIRCUIT FOR SWITCHING TESTS

NOTE: Mode control and  $\overline{R}$  inputs are low and unused  $\overline{S}$  input is high.

FIGURE 2-INITIATING AND TERMINATING PULSE TRAIN FROM S INPUTS

TTL DEVICES

PARAMETER MEASUREMENT INFORMATION

NOTE: At least one of the  $\overline{S}$  inputs is low.

FIGURE 4-INITIATING AND TERMINATING PULSE TRAIN WITH MODE CONTROL INPUT

NOTE: Input  $\overline{R}$  is low and the unused  $\overline{S}$  input is high.

FIGURE 5-ENABLING SINGLE PULSE

Υ.

3-469