# MONOSTABLE MULTIVIBRATOR

N74121

N74121-A,F

### DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

This monolithic TTL monostable multivibrator features d-c triggering from positive or gated negative-going inputs with inhibit facility. Both positive and negative-going output pulses are provided with full fan-out to 10 normalized loads.

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. Schmitt-trigger input circuitry for the B input allows jitter-free triggering from inputs with transition times as slow as 1 volt/second, providing the circuit with an excellent noise immunity of typically 1.2 volts. A high immunity to  $V_{CC}$  noise of typically 1.5 volts is also provided by internal latching circuitry.

Once fired, the outputs are independent of further transitions on the inputs and are a function only of the timing components. Input pulses may be of any duration relative to the output pulse. Output pulse lengths may be varied from 40 nanoseconds to 40 seconds by choosing appropriate timing components. With no external timing components (i.e., pin 9 connected to pin 14, pins 10, 11 open) an output pulse of typically 30 nanoseconds is achieved which may be used as a dc triggered reset signal. Output rise and fall times are TTL compatible and independent of pulse length.

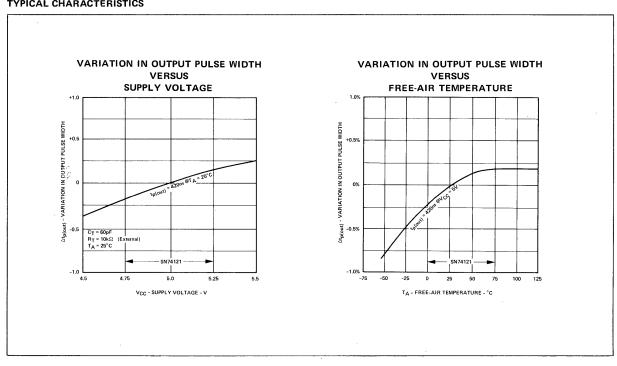

Pulse width is achieved through internal compensation and is virtually independent of  $V_{\mbox{\footnotesize{CC}}}$  and temperature. In most applications, pulse stability will only be limited by the accuracy of external timing components.

Jitter-free operation is maintained over the full temperature and V<sub>CC</sub> range for more than six decades of timing capacitance (10 pF 10 $\mu F$ ) and more than one decade of timing resistance (2k $\Omega$  to 40k $\Omega$ ). Throughout these ranges, pulse width is defined by the relationship  $t_{p(out)} = C_T R_T \log_e 2$ .

Circuit performance is achieved with a nominal power dissipation of 90 milliwatts at 5 volts (50% duty cycle) and a quiescent dissipation of typically 65 milliwatts.

Duty cycles as high as 90% are achieved when using  $R_T$  -  $40k\Omega$ . Higher duty cycles are achievable if a certain amount of pulse-width jitter is allowed.

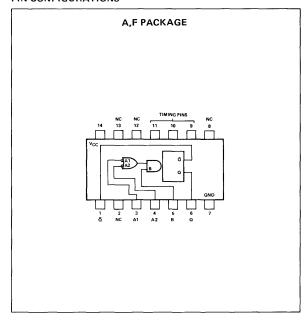

#### PIN CONFIGURATIONS

### **TRUTH TABLE**

| t <sub>n</sub> INPUT |    |   | t <sub>n+1</sub> INPUT |    |   |          |  |

|----------------------|----|---|------------------------|----|---|----------|--|

| A1                   | A2 | В | A1                     | A2 | В | OUTPUT   |  |

| 1                    | 1  | 0 | 1                      | 1  | 1 | Inhibit  |  |

| 0                    | ×  | 1 | 0                      | ×  | 0 | Inhibit  |  |

| ×                    | 0  | 1 | ×                      | 0  | 0 | Inhibit  |  |

| 0                    | ×  | 0 | 0                      | ×  | 1 | One Shot |  |

| ×                    | 0  | 0 | ×                      | 0  | 1 | One Shot |  |

| 1                    | 1  | 1 | ×                      | 0  | 1 | One Shot |  |

| 1                    | 1  | 1 | 0                      | ×  | 1 | One Shot |  |

| ×                    | 0  | 0 | ×                      | 1  | 0 | Inhibit  |  |

| 0                    | ×  | 0 | 1                      | ×  | 0 | Inhibit  |  |

| ×                    | 0  | 1 | 1                      | 1  | 1 | Inhibit  |  |

| 0                    | ×  | 1 | 1                      | 1  | 1 | Inhibit  |  |

| 1                    | 1  | 0 | ×                      | 0  | 0 | Inhibit  |  |

| 1                    | 1  | 0 | 0                      | ×  | 0 | Inhibit  |  |

$1 = V_{in(1)} \ge 2V$

$0 = V_{in(0)} \le 0.8V$

- 1. A1 and A2 are negative-edge-triggered logic inputs, and will trigger the one shot when either or both go to logical 0 with B at logical 1.

- 2. B is a positive Schmitt-trigger input for slow edges or level detection, and will trigger the one shot when B goes to logical 1 with either A1 or A2 at logical 0. (See Truth

- 3. External timing capacitor may be connected between pin (10) (positive) and pin (11). With no external capacitance, an output pulse width of 30ns is obtained typical-

- 4. To use the internal timing resistor ( $2k\Omega$  nominal), con-

- To obtain variable pulse width connect external variable resistance between pin (9) and pin (4). No external current limiting is needed.

- 6. For accurate repeatable pulse widths connect an external resistor between pin 11 and pin 14 with pin (9) open-circuit.

- 7.  $t_n = time before input transition.$

- 8.  $t_{n+1}$  = time after input transition.

- 9. x indicates that either a logical 0 or 1, may be present.

# SIGNETICS DIGITAL 54/74 TTL SERIES - N74121

### RECOMMENDED OPERATING CONDITIONS

|                                                                      | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> :                                     |      |     |      | V    |

| N74121 Circuits                                                      | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out from each Output, N                               |      |     | 10   | 1    |

| Input Pulse Rise/Fall Time: Schmitt Input (B)                        |      |     | 1    | V/s  |

| Logic Inputs (A1, A2)                                                |      |     | 1    | V/μs |

| Input Pulse Width                                                    | 50   |     |      | ns   |

| External Timing Resistance Between Pins (11) and (14) (Pin (9) open) | 1.4  |     |      | kΩ   |

| External Timing Resistance: S54121                                   | 1    |     | 30   | kΩ   |

| N74121                                                               | 1    |     | 40   | kΩ   |

| Timing Capacitance                                                   | 0    |     | 1000 | μF   |

| Output Pulse Width                                                   |      |     | 40   | s    |

| Duty Cycle: $R_T = 2k\Omega$                                         | ĺ    |     | 67%  |      |

| $R_T = 30k\Omega$ (\$54121) or                                       |      |     | 90%  |      |

| $R_T = 40k\Omega (N74121)$                                           |      |     |      |      |

# ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER           |                                                                   | TE                     | TEST CONDITIONS*           |        |     | TYP** | MAX  | UNIT  |

|---------------------|-------------------------------------------------------------------|------------------------|----------------------------|--------|-----|-------|------|-------|

| v <sub>T</sub> +    | Positive-going threshold voltage at A input                       | V <sub>CC</sub> = MIN  |                            |        |     | 1.4   | 2    | v     |

| ν <sub>T</sub> -    | Negative-going threshold voltage at A input                       | V <sub>CC</sub> = MIN  |                            |        | 0.8 | 1.4   |      | \ \   |

| V <sub>T</sub> +    | Positive-going threshold voltage at B input                       | VCC = MIN              |                            |        |     | 1.55  | 2    | \ \ \ |

| V <sub>T</sub> -    | Negative-going threshold voltage at B input                       | V <sub>CC</sub> = MIN  |                            |        | 0.8 | 1.35  |      | \ \   |

| Vout (0)            | Logical 0 output voltage                                          | V <sub>CC</sub> = MIN, | I <sub>sink</sub> = 16mA   |        |     | 0.22  | 0.4  | V     |

| Vout (1)            | Logical 1 output voltage                                          | V <sub>CC</sub> = MIN, | I <sub>load</sub> = -400μΑ |        | 2.4 | 3.3   |      | V     |

| <sup>1</sup> in (0) | Logical 0 level input current at A <sub>1</sub> of A <sub>2</sub> | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0.4V     |        |     | -1    | -1.6 | mA    |

| <sup>1</sup> in (0) | Logical 0 level input current at B                                | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0.4V     |        |     | -2    | -3.2 | mA    |

|                     | Logical 1 level input                                             | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V     |        |     | 2     | 40   | μΑ    |

| <sup>l</sup> in (1) | current at A <sub>1</sub> of A <sub>2</sub>                       | V <sub>CC</sub> = MAX, | $V_{in} = 2.4V$            |        | ļ   | 0.05  | 1    | mA    |

| 1                   | Logical 1 level input                                             | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V     |        |     | 4     | 80   | μΑ    |

| <sup>l</sup> in (1) | current at B                                                      | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 5.5V     |        |     | 0.05  | 1    | mΑ    |

|                     | Short circuit output                                              |                        |                            | S54121 | -20 | -25   | -55  | mA    |

| los                 | current at Q or $\overline{\mathbf{Q}}^{\dagger}$                 | V <sub>CC</sub> = MAX  |                            | N74121 | -18 | -25   | -55  | m.A   |

| <sup>1</sup> cc     | Power supply current in quiescent (unfired) state                 | V <sub>CC</sub> = MAX  |                            |        |     | 13    | 25   | mA    |

| <sup>1</sup> cc     | Power supply current in fired state                               | V <sub>CC</sub> = MAX  |                            |        |     | 23    | 40   | m.A   |

### SWITCHING CHARACTERISTICS, $V_{CC} = 5V$ , $T_{\Delta} = 25^{\circ}C$

| PARAMETER           |                                                                                           | TE                                               | MIN                                                | TYP | MAX | UNIT |    |

|---------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|-----|-----|------|----|

| <sup>t</sup> pd1    | Propagation delay time to<br>logical 1 level from B input<br>to Q output                  | C <sub>L</sub> = 15pF,                           | C <sub>T</sub> = 80pF                              | 15  | 35  | 55   | ns |

| <sup>t</sup> pd1    | Propagation delay time to<br>logical 1 level from A1/A2<br>inputs to Q output             | C <sub>L</sub> = 15pF,                           | C <sub>T</sub> = 80pF                              | 25  | 45  | 70   | ns |

| <sup>t</sup> pd0    | Propagation delay time to logical 0 level from B input to $\overline{\mathbf{Q}}$ output  | C <sub>L</sub> = 15pF,                           | C <sub>T</sub> = 80pF                              | 20  | 40  | 65   | ns |

| <sup>t</sup> pd0    | Propagation delay time to logical 0 level from A1/A2 inputs to $\overline{\Omega}$ output | C <sub>L</sub> = 15¢F,                           | C <sub>T</sub> = 80pF                              | 30  | 50  | 80   | ns |

| t <sub>p(out)</sub> | Pulse width obtained using internal timing resistor                                       | C <sub>L</sub> = 15pF,<br>R <sub>T</sub> = Open, | $C_T = 80pF$<br>Pin 9 to $V_{CC}$                  | 70  | 110 | 150  | ns |

| <sup>t</sup> p(out) | Pulse width obtained with zero timing capacitance                                         | C <sub>L</sub> = 15pF,<br>R <sub>T</sub> = Open, | $C_T = 0.$ Pin 9 to $V_{CC}$                       | 20  | 30  | 50   | ns |

| <sup>t</sup> p(out) | Pulse width obtained using external timing resistor                                       | $C_L = 15pF,$<br>$R_T = 10k\Omega$               | $C_T = 100pF$ ,<br>Pin $9$ Open                    | 600 | 700 | 800  | ns |

| <sup>t</sup> p(out) | Pulse width obtained using external timing resistor                                       | $C_L = 15pF,$<br>$R_T = 10k\Omega$               | $C_T = 1 \mu F$ ,<br>Pin(9)Open                    | 6   | 7   | 8    | ms |

| <sup>t</sup> hold   | Minimum duration of trigger pulse                                                         | C <sub>L</sub> = 15pF,<br>R <sub>T</sub> = Open, | C <sub>T</sub> = 80pF,<br>Pin 9 to V <sub>CC</sub> |     | 30  | 50   | ns |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

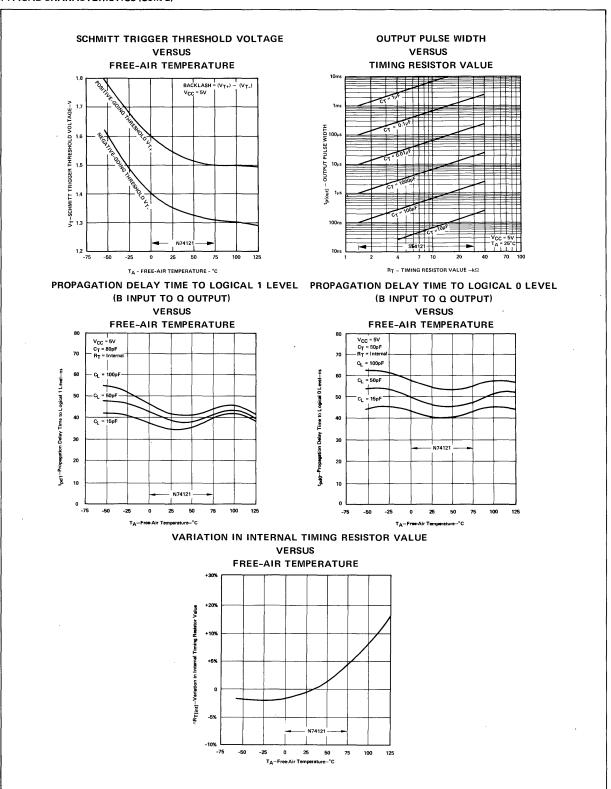

### TYPICAL CHARACTERISTICS

<sup>\*\*</sup> All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

† Not more than one output should be shorted at a time.

#### TYPICAL CHARACTERISTICS (Cont'd)